Projects

Transmitting Images Over SDRs With GNU Radio and Simulink

Used raspberry pi SDRs to compare different modulation schemes(BPSK, QPSK, 16QAM) to find the maximum distance they could send an image to another SDR using GNU Radio and Simulink.

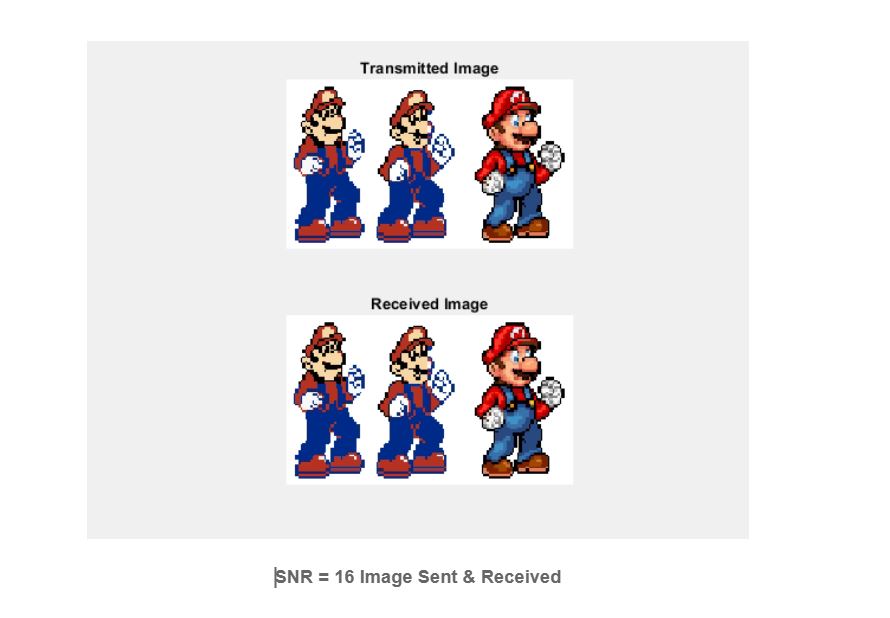

First image is sending an image over air to another SDR using BPSK

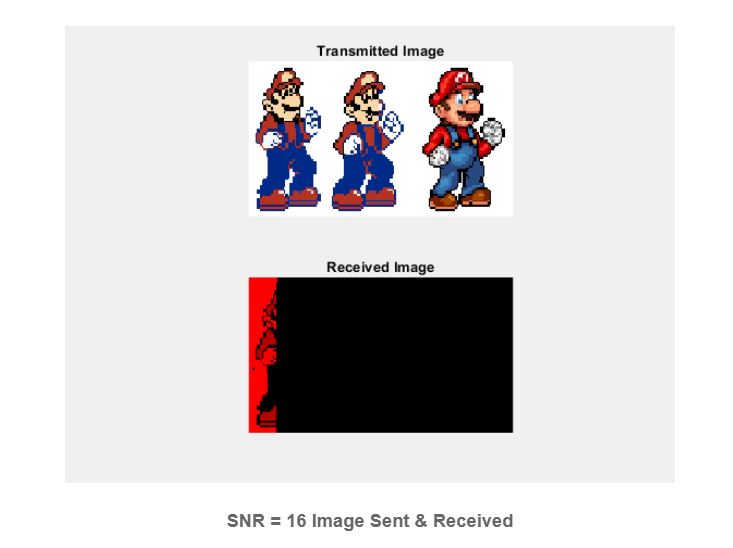

Second image is sending an image over air to another SDR using 16QAM (Not performing well because of the smaller decision boundaries)

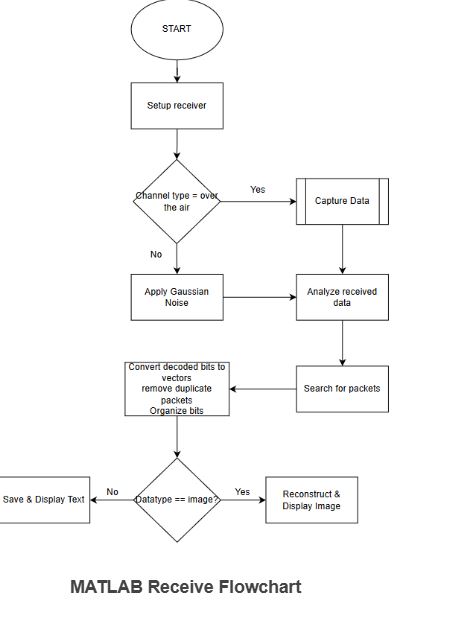

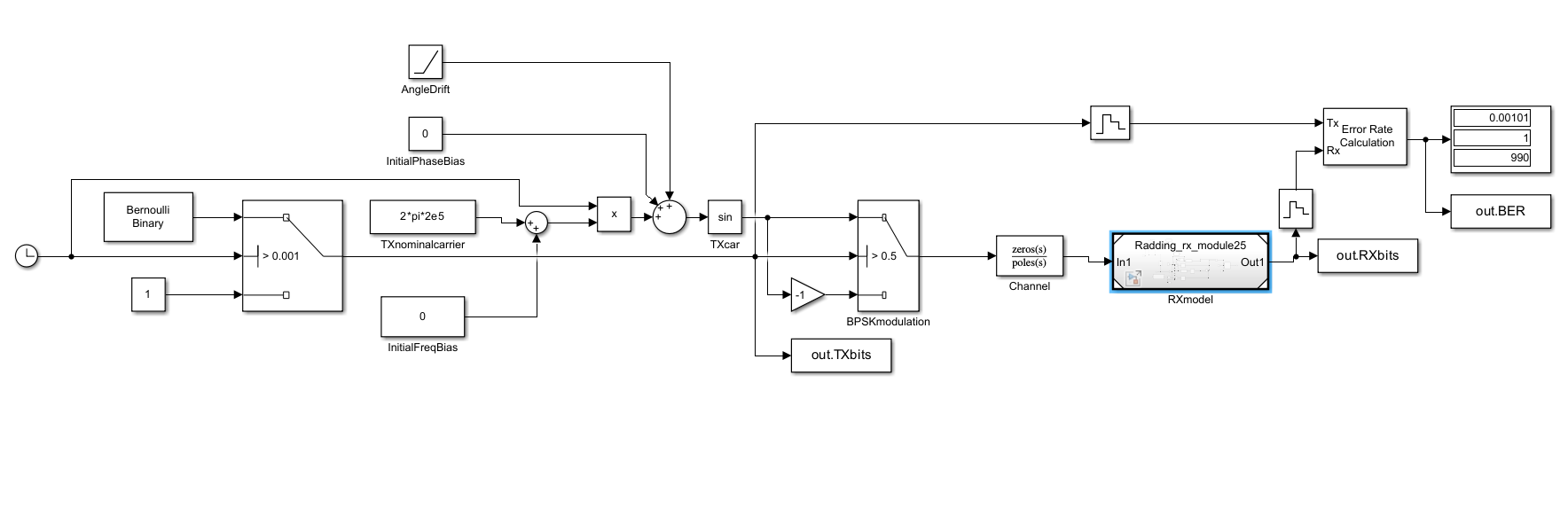

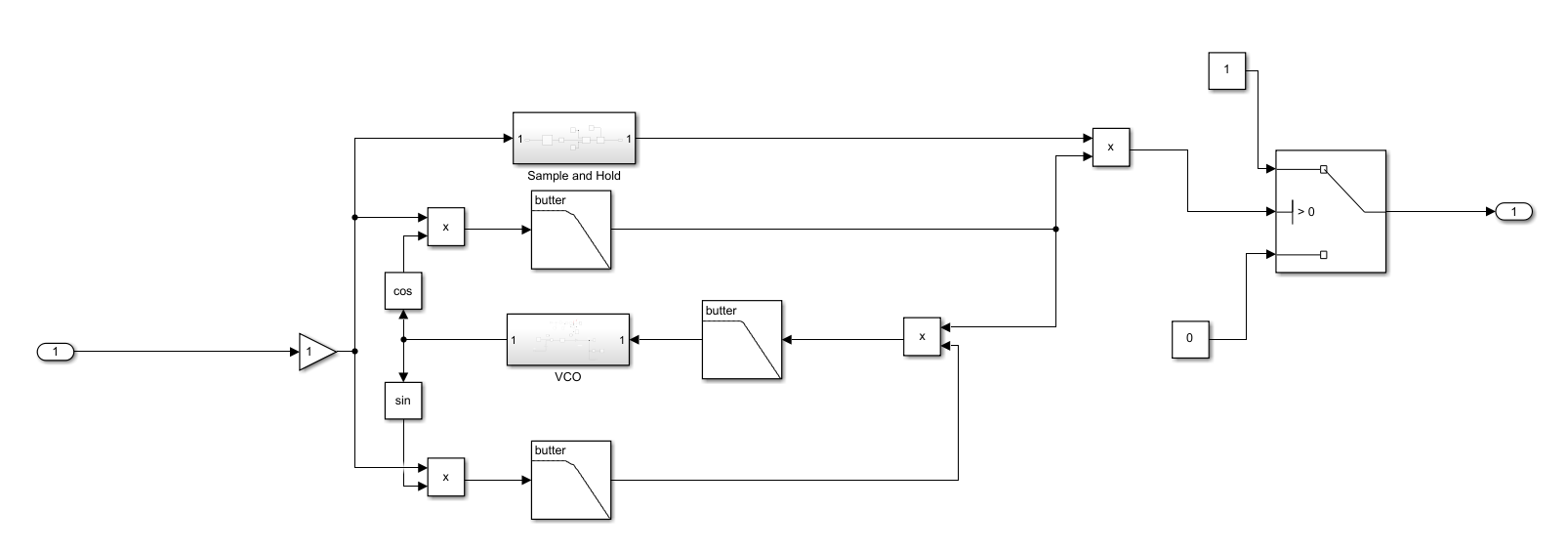

Third and fourth images are the code flow diagrams of the transmitter and receiver

Additional Resources:

Download Lab Notebook (PDF)

Download SDR Modulation Final Report (PDF)

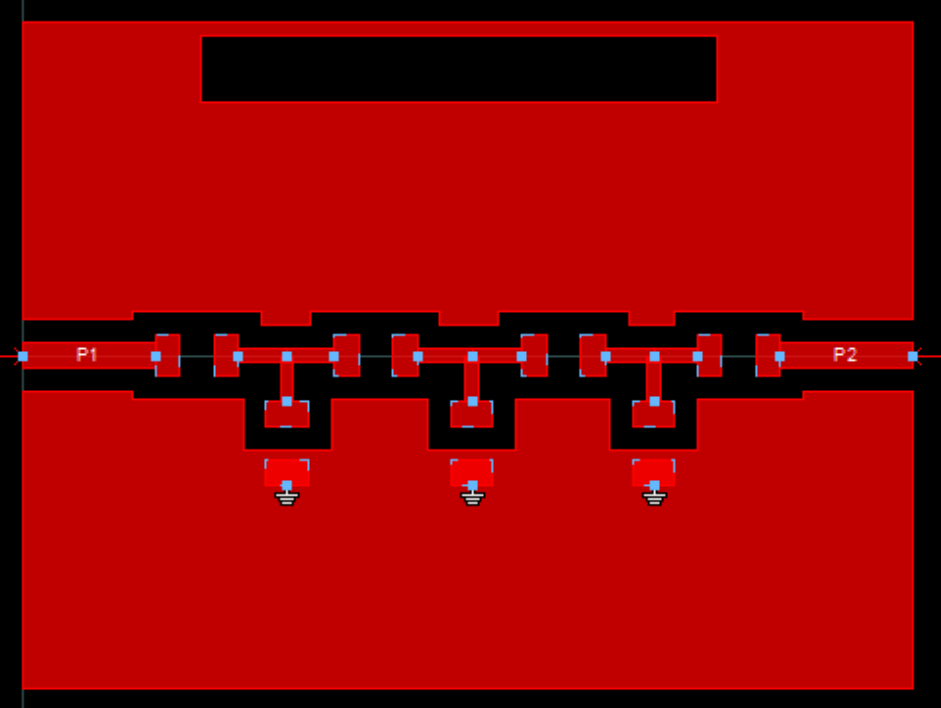

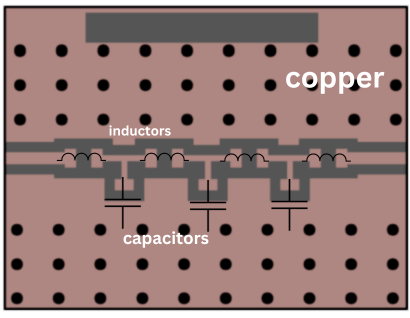

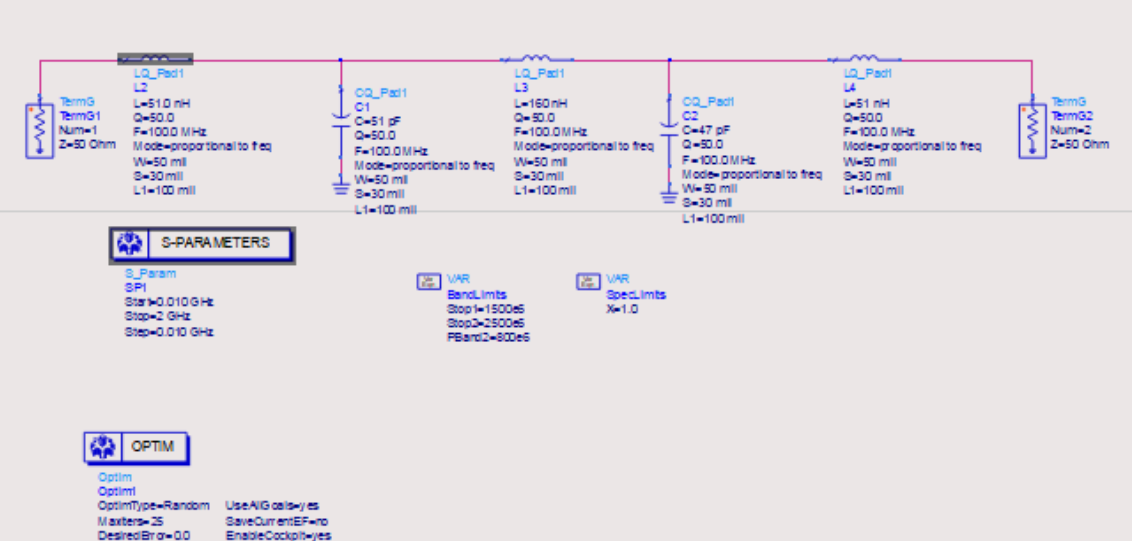

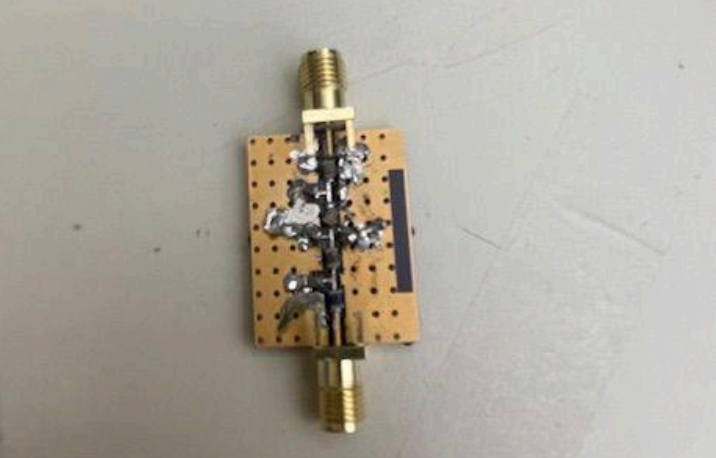

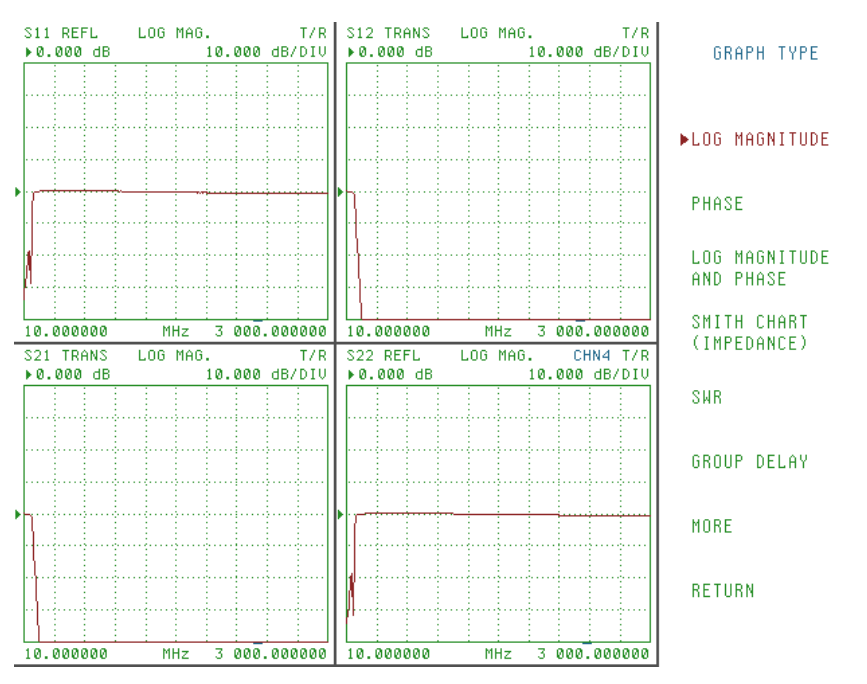

10 MHz Low Pass Filter Simulation

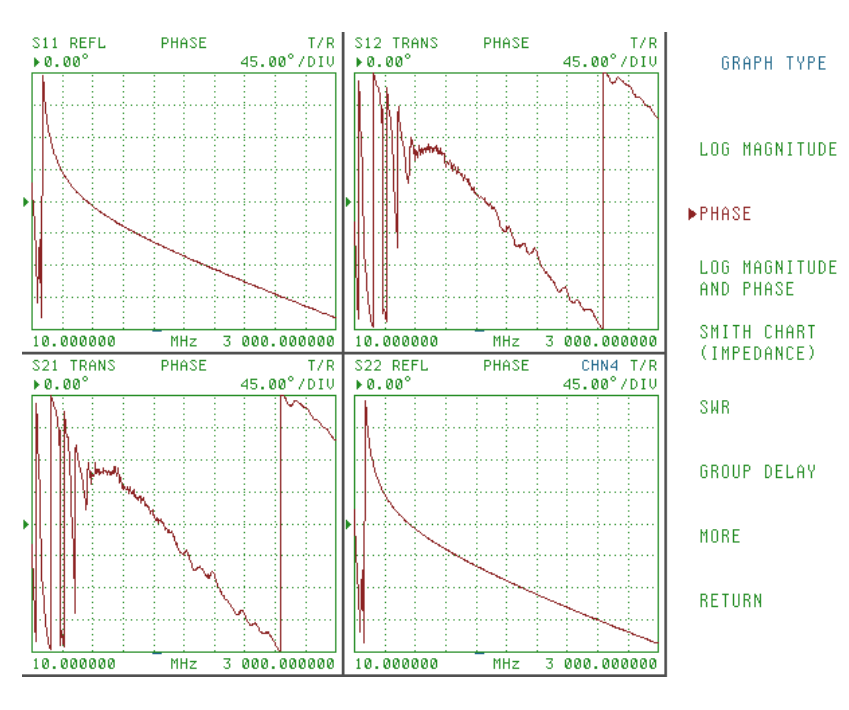

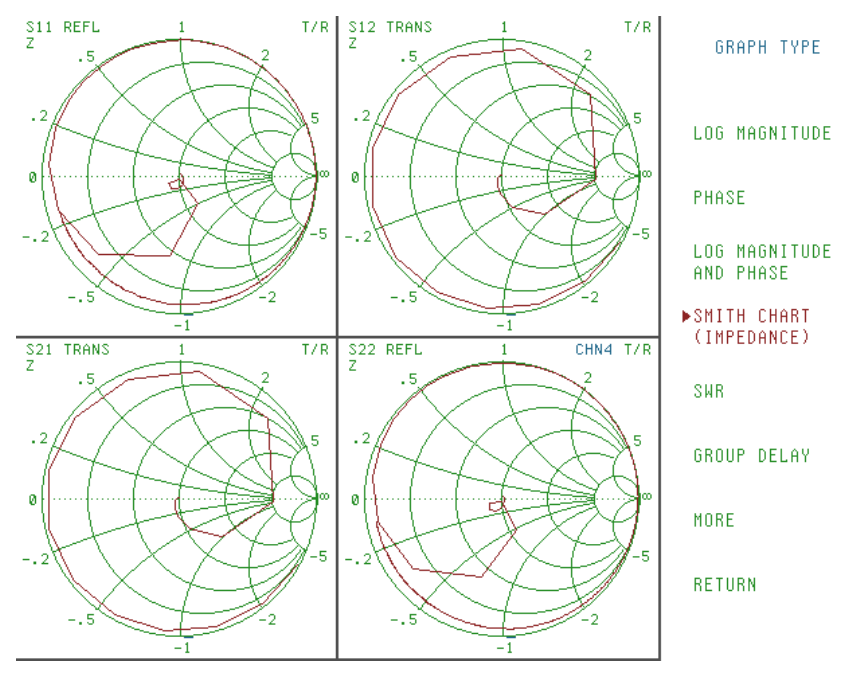

Here is a 10 MHz low pass filter built in Keysight ADS. The filter was ordered on Oshpark PCB and had its S-parameters magnitude and phase tested on a VNA. Impedance was also tested. Use the arrows below to navigate through the simulation and results images.

Additional Resources:

Download Full Project Details (PDF)

Simulink Costas Loop BPSK

A receiver was designed to synchronize and demodulate 10 kbps data modulated using BPSK with a nominal 200 kHz carrier. The transmitter consistently begins with a pilot signal consisting of ten consecutive '1' bits, followed by the data stream.

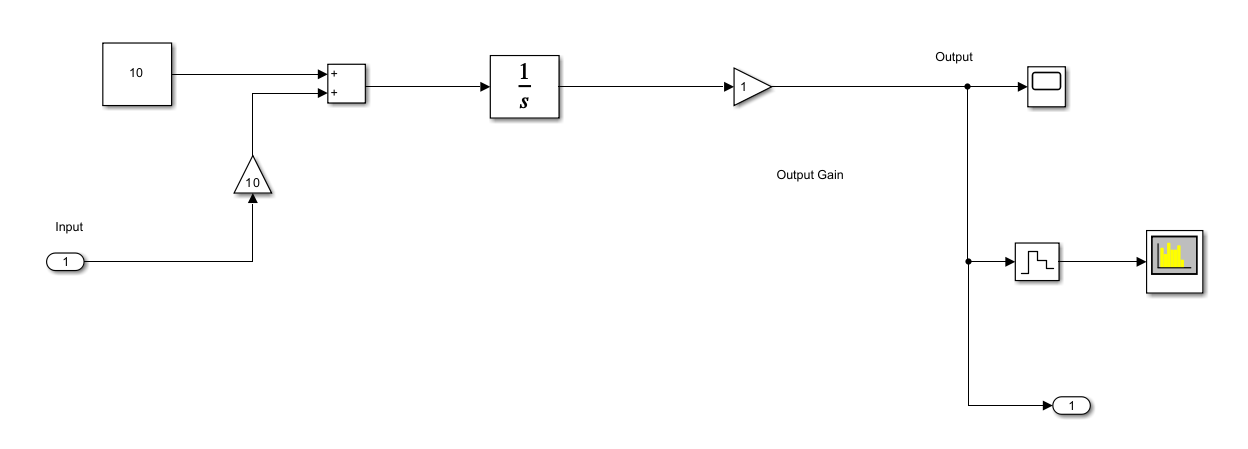

In the first image, a test harness is shown with configurable parameters, allowing adjustments to phase, frequency, and angle drift. The second image illustrates a Costas loop, implemented to correct frequency bias and phase offset. The Costas loop locks onto the signal’s center frequency, downconverting it to baseband by generating a local, in-phase replica of the carrier, multiplying it with the received signal, and then filtering the result through a low-pass filter.

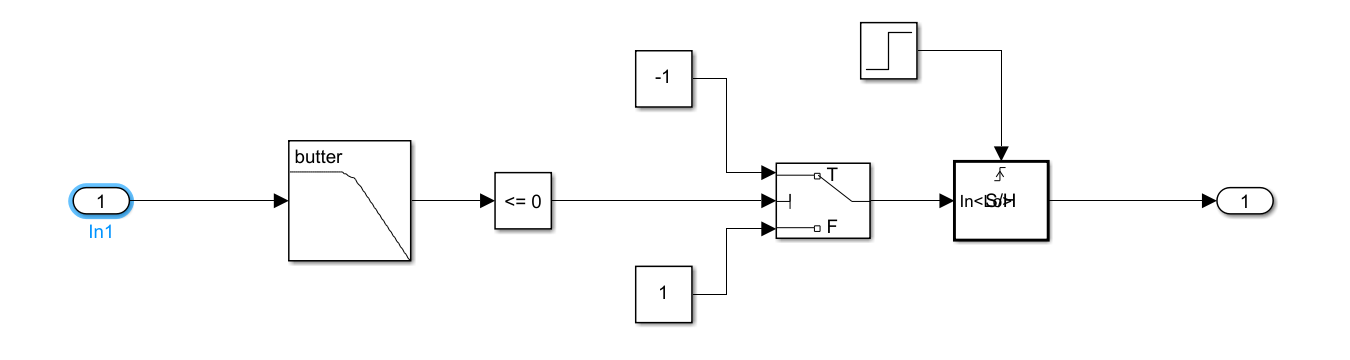

The third image depicts a voltage-controlled oscillator (VCO) that generates a local carrier signal aligned with the phase of the received signal. The fourth image shows a sample-and-hold system designed to detect the pilot signal, triggering the receiver to process the incoming data once the pilot is successfully identified.

Blog

Check out my latest posts and updates: